Process focused on understanding impacts on performance,

understanding basics of what may happen if something is incorrect or

pushing a design limit, and knowing what to consider and ask for when

working with designers on issues and improvements.

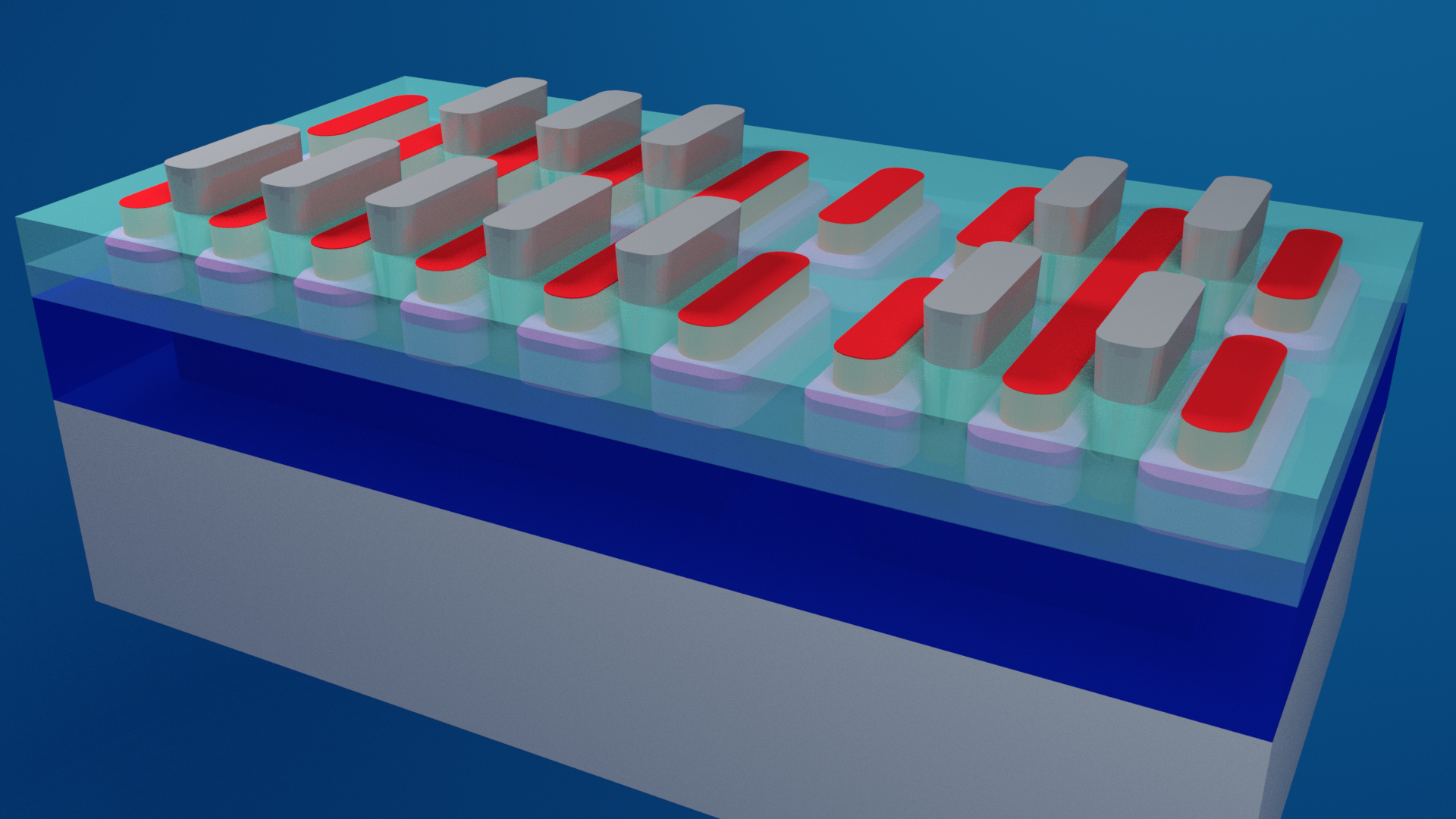

Learning Objectives: Understand how processing at the transistor level relates to product behavior, understand the basics of process modules such as isolation, implant and anneal, strain engineering, Hi-K metal gates, contacts, copper interconnect and Low-K dielectrics impact the performance and yield of a process. Understand how layout and process flow relate to the design process. Understand how lithography impacts yield and performance.

Learning Objectives: Understand how processing at the transistor level relates to product behavior, understand the basics of process modules such as isolation, implant and anneal, strain engineering, Hi-K metal gates, contacts, copper interconnect and Low-K dielectrics impact the performance and yield of a process. Understand how layout and process flow relate to the design process. Understand how lithography impacts yield and performance.