One of the most important aspects of any manufacturing effort is the yield of the process. Today, the investment in facilities, equipment and materials is so high that consistently high yields are vital to the profitability of the semiconductor manufacturer. Furthermore, the engineers must get to that consistent high yield as quickly as possible to avoid product delays.

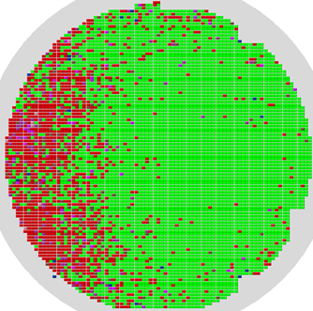

Solving a yield issue requires complex pattern recognition skills using limited amounts of data. While fab tools and test equipment generate terabytes of data, knowing what to look for in that mountain of data is a difficult task. Typically, one needs to start with a big picture understanding, by identifying what is failing (failure mode of the IC), and how the failure manifests itself in the process (spatial dependencies, lot dependencies, equipment dependencies, etc.). The engineer must then formulate hypotheses that fit the "what" and "how". He or she would then look through the data at hand to try and confirm or deny each hypothesis. If there is insufficient data to do this, one may have to gather additional data. Finally, if there is no data on hand that can conclusively prove an hypothesis, then the engineer would typically submit a sample of ICs for failure analysis to help provide greater understanding of the problem. Once the engineering team identifies the source of the problem, they will develop a fix and implement the fix on a set of control material. This course walks through the basics of the yield analysis process, including yield models, methods to visualize yield-related data, and techniques for solving yield-related issues.

One of the most important aspects of any manufacturing effort is the

yield of the process. Today, the investment in facilities, equipment

and materials is so high that consistently high yields are vital to the

profitability of the semiconductor manufacturer. Furthermore, the

engineers must get to that consistent high yield as quickly as possible

to avoid product delays.

One of the most important aspects of any manufacturing effort is the

yield of the process. Today, the investment in facilities, equipment

and materials is so high that consistently high yields are vital to the

profitability of the semiconductor manufacturer. Furthermore, the

engineers must get to that consistent high yield as quickly as possible

to avoid product delays.

Solving a yield issue requires complex

pattern recognition skills using

limited amounts of data. While fab tools and test equipment generate

terabytes of data, knowing what to look for in that mountain of data is a

difficult task. Typically, one needs to start with a big picture

understanding, by identifying what is failing (failure mode of the IC),

and how the failure manifests itself in the process (spatial

dependencies, lot dependencies, equipment dependencies, etc.). The

engineer must then formulate hypotheses that fit the "what" and "how".

He or she would then look through the data at hand to try and confirm or

deny each hypothesis. If there is insufficient data to do this, one

may have to gather additional data. Finally, if there is no data on

hand that can conclusively prove an hypotheses, then the engineer would

typically submit a sample of ICs for failure analysis to help provide

greater understanding of the problem. Once the engineering team

identifies the source of the problem, they will develop a fix and

implement the fix on a set of control material. This course walks

through the basics of the yield analysis process, including yield

models, methods to visualize yield-related data, and techniques for

solving yield-related issues.

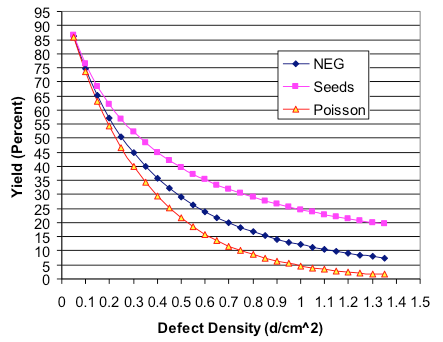

Models are an important component of the yield analysis problem. We need models to predict not only the yield of new products, but also provide clues as to what types of problems might be occurring with a wafer lot or group of lots. This course covers general models for yield like the Poisson Yield Model, the Seeds Model and others. It also covers various techniques and approaches to predicting yield based on measured electrical and physical parameters.

This course material covers the procedures associated with Yield Analysis. We cover procedures and methods that are used to help improve yield. These can be techniques used at the design level as well as techniques to address yield problems that are currently occurring.